The Programmable Network

Product Briefs - Related Products

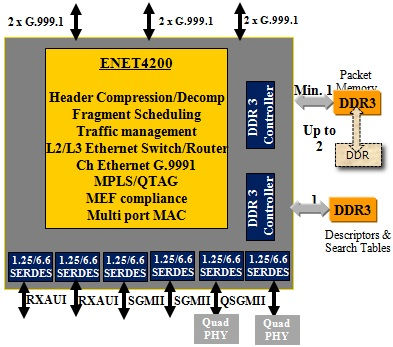

ENET 4200 - Radio Access Packet Engine

Features

-

20 Gbps Carrier Ethernet Switch integrating flexible interfaces up to 20Gbps including XFI, RXAUI, SGMII, RGMII

-

20 Gbps Fabric Flow Processor , integrating Carrier Ethernet Switch, MPLS-TP, Hierarchical Queuing and scheduling, CFM/OAM through internal OAM processor offload, Programmable Header compression , G.999.1 and EFM bonding and protocol interworking all integrated on a single 28nm FPGA Xilinx 's Kintex 7 FPGA

-

Eight 10G integrated SERDES

-

Data Interfaces: XFI, QXAUI, QSGMII ( 4 x GbE) , SGMII, 6 to 16 x G.999.1 RGMII, and MII.

-

On the fly encapsulation and packet anaylizing

-

Classify streams based on five configurable fields with five hierarchies

-

Supports 100ms deep buffering for radio access

-

Ch Ethernet G.999.1 to support fragmentation and fragment scheduling over Radio links or G.vector DSL ports

-

L2/L3/L4 header compression / decompression

-

Supports 16K flows, 16K policers, 16K shapers, 16K queues and 1k Virtual ports enable full Ethernet switching between all 1k Virtual ports

-

Full compliance to TR-101, MEF standards including compliance with MEF 9 and MEF 14, 802.1ad, 802.1ah, 802.1ag, Y.1731, E-LAN, E-Line, MPLS-TP, Provide Bridge, and PBB.

-

Deterministic 20Gbps throughput

-

Integrated OAM Hardware processor with Programmable Packet Generator and analyzer

-

EFM bonding supporting 16 EFM bonding groups , configurable to 2, 4, or 8 ports per group.

-

1588v2 TC/BC/OC and Sync E

-

Huge parameter search engine data base through a single DDR2, supporting up 256,000 entries including 256,000 MAC address or IP for L2&L3 switching and routing, multicast, classification tables and 32 programmable search tables

-

Hierarchical QoS including WFQ, WRR, WRED and strict priority supporting up to 16K queues

-

MEF 10 compliance policing per stream with 64Kbps granularity

-

Advanced hierarchical classification and filtering including configurable packet parsing and configurable search keys

-

Programmable Packet Editor supporting per flow multiple actions of Append/ Swap/ Extract/ stamp in any preconfigured location in the first 128 bytes

-

Management is performed through , generic CPU interface, MII, GMII or integrated CPU

Description:

The ENET4200 20Gbps Access Flow Processor is a family of high performance configurable flow processor and traffic manager solutions optimized for the Metro Access Market. The ENET 4200 is tailured to provide best carrier Ethernet packet engine for Radio Access, through the support of G.999.1 standard fragmentation, fragment ( vs frame) scheduling over the radio, and header compression.

The ENET4200 design is based on an extremely efficient architecture resulting in 80% die size reduction, enabling an extremely cost effective implementation based on low cost FPGAs.

The Ethernity ENET4200 solution retains the flexibility and programmability of FPGAs, while providing a solution that is cost and power competitive with ASIC solutions. ENET is based on atomic engines pipeline architecture, and supports performance of up to 20Gbps on ultra low cost FPGA, with software configurable L2 to L4 protocol interworking, hierarchical multi field classification and flow Identification, Virtual Ethernet Switch used for VPLS, E-LAN , E-TREE and E-Line, Hierarchical policing, Header compresion, performance monitoring, packet editing, Hierarchical scheduling and shaping .

The ENET4200 protocol interworking includes software support for packet editing, which provide the ability to receive packets in any format and change the protocol per virtual output port to any other protocol, hence it supports Ethernet II, SNAP, Q-in-Q, PBB, MPLS-TP,GRE, L2TP, and other programmed by the user.

Detailed Features:

Classification

-

Identifies flow and assign several flow IDs per stream, based on 36 flexible /programmable fields including TCP, UDP, IP address, MAC, port number, L2 header, LSP, or based on information available in the first 128 bytes of each frame

-

Assigns packet priority based on Ingress priority mapping configuration.

-

Up to 32K flows filter for any classified packet based on the set of rules and set of the 64 configurable fields

Switching and Routing

-

Fully IEEE 802.1Q compliant Ethernet switch with up to 256K Ethernet MACs, and 16K Active Network TAGs/streams comprising from VLANs, AAL5, QTAG, MPLS or other packet fields programmed by the software and up to 4K Multicast groups.

-

Configuration forwarding/switching decision per flow including connection oriented , L2, L3 or L4 forwarding decision

-

32 software programmable / configurable search tables

-

Configurable forwarding key and learning key per flow

-

Force association of specific MAC to a certain logical port and service.

-

16K L3 address for supporting L3 forwarding

-

Partitioning of MAC address per VPNL2

-

Control packets classifier for both user and Network L2 control protocol packets

-

Flexible forward decision per port per protocol with the ability to forward transparently, to CPU or Discard

-

Support include ARP, DHCP, IGMPv2, IGMPv3 and other based on flexible configuration options

Quality of Service (QoS)

-

Hierarchical QoS with 3-5 hierarchies

-

Eight priority queues per virtual port

-

Priority Assignment per Port, 802.1p tag, MPLS (LLSP or ELSP), L3 DiffServe Code Point (DSCP) or TOS

-

Configurable L3/L2 Priority profiles per portIngress and Egress priority mapping per flow

-

Ingress and Egress priority mapping per flow

Policing and Shaping

-

Extended Metering according to Three Color scheme as defined by MEF 10 including color aware and coupling flag modes configured per flow

-

Supports up to 16K flows

-

Each ingress and egress flow can be configured in a granularity of 64Kbps up to 100Mbps

Traffic Management

-

Support of Jumbo frames up to 16KB

-

Supports four-eight priority queues per port / logical port

-

Programmable values for drop level

-

Strict priority and dedicated low jitter scheduling

-

Supports eight priority queues per port / virtual port

-

4 scheduing hierarchies

-

Programmable values for drop level.

-

Two Weighted Fair Queuing hierarchies

-

TCP Friendly Algorithm implemented

Packet Editing

-

Extract, append, or swap in the egress any type of Layer 2/3/4 headers programmed by software, including, Q-In-Q, PPPoE, PPPoA, ATM to Ethernet (AAL5), PPP, HDLC, L2TP,L3, or any other header up to 128 bytes, controlled and configured by software.

-

L2 and L3 loop backs including swap of MAC SA and DA, Swap of IP.

-

Stamp data at the bit/byte level anywhere within the first 128 bytes including priority remapping, bytes count, sequence ID and DSCP.

OAM/CFM

-

Integrated packet generator and analyzer to support OAM packet per MEF 17, Y.1731, and 802.1ag, 802.3 ah including per flow BERT

-

Rate limitation and filtering of OAM messages and other BPDUs to prevent network attacks

-

L2/L3/L4 control packets classifier for both user and network L2 control protocol packets per flow

-

Hardware processing for L2, L3 Loop backs (swap L2 SA/DA, swap L3 SA/DA)

-

Fast protecting switching within micro seconds

-

ELPS G.8031, ERPS G.8032

-

802.3ah Link OAM

- Link loopback

- Unidirectional link fault detection

- Threshold-based monitoring and notification

-

802.1ag end-to-end Service OAM and CFM

- Supports 64 levels of maintenance domains and Maintenance End Points (MEP)

- Up to 512 Maintenance Associations

- Connectivity Check Messages (CCM)

- Remote Defect Indication (RDI)

- Link trace

- Diagnostic loopback

-

Integrate packet generator and analyzer to support generation and analyzing of OAM packets and full support for Y.1731

-

Y.1731 Performance Monitoring

- Frame delay

- Frame delay variation (jitter)

- Frame loss — AIS

EFM bonding & Fragmentation

-

Supports Ethernet Fragmentation per G.999.1 to enable prioritization of short packet and jumbo packets over Radio links

-

Enable connectivity to g.vector DSL components

-

EFM bonding supporting 16 bonding groups

-

Supports 6 to 16 G.999.1 Channelized Ethernet ports

Header Compression

-

Supports L2/L3/L4 header compression / decompression of the first 128 B of the packet

-

End to end automatic learning of original packet type

Synchronization over Packet

-

1588 End to End Transparent Clock1588v2

-

Slave mode clock recovery through third part software

-

Synchronous Ethernet

L2 Control Protocol

-

L2 Control packets classifier for both user and Network L2 control protocol packets

-

Flexible forward decision per port/flow per Protocol with the ability to forward transparently, to CPU or Discard

-

OAM packets classifier for both user and Network including support for 802.1ag

-

Flexible forward decision per port per OAM type with the ability to forward transparently, to CPU or Discard

IGMP Proxy

-

IGMP V2 and V3 compliance

-

IGMP packet snooping to processor in the U/S direction

-

Forwarding and multicast classification based on Source IP and Destination IP

DDR SDRAM Interface

-

External 16-bit DDR2-SDRAM 400 MHz interface

-

Supports 128/256/512Mbit 16 bit width standard PC DDR2 SDRAM components

Host CPU Interface

-

OptionMotorola PowerPC 1&2 Glueless interface

-

Up to 66Mhz with 8/16/32 bit bus width

-

MII interface

Interfaces

Flexible up to 20Gbps

Reference Design Kit